差分逻辑电平——SSTL、HSTL、HSUL结构-程序员宅基地

SSTL/HSTL/HSUL

属于DDR存储器接口逻辑电平,虽然是单端,本质上是差分对,因实现机制是将信号与参考电平Vref组成差分对进行比较。

-

SSTL

SSTL:Stub Series Termination Logic,短截线串联端接逻辑。

我们所熟知的DDR 采用的就是这个标准。这个电平标准看着似乎有点陌生,但其实它经常会被使用,只是我们平时关注的比较少。这就比较奇怪了,用的多自然会关注比较多,为什么反而关注比较少呢?因为SSTL电平一般用在DDR SDRAM存储接口上,一般CPU和DDR颗粒都是默认标准的SSTL电平,不需要我们再去做电平匹配的检查,但该电平标准与DRAM接口有绑定关系,所以该逻辑电平与DRAM的标准协议相关:

1. SSTL25 I/O标准用于DDR SDRAM存储器接口;

2. SSTL18 I/O标准用于DDR2 SDRAM存储器接口,1V8电源;

3. SSTL15 I/O标准用于DDR3 SDRAM存储器接口,1V5电源;

4. SSTL135 I/O标准用于DDR3L SDRAM存储器接口,1V35电源;

5. SSTL12支持DDR4 SDRAM存储器接口,1V2电源;

6. DDR5 SDRAM存储器接口支持PODL电平(1.1V)。

目前有两个标准,CLASS-1和CLAS-2

CLASS-1只有输入有戴维南模式,输出没有,且只支持单向传输。

CLASS-2输出和输出都支持戴维南模式,且支持双向传输。

- 基本电路结构

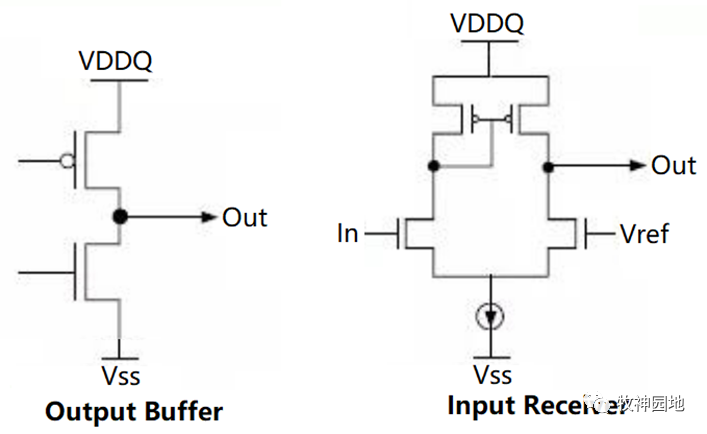

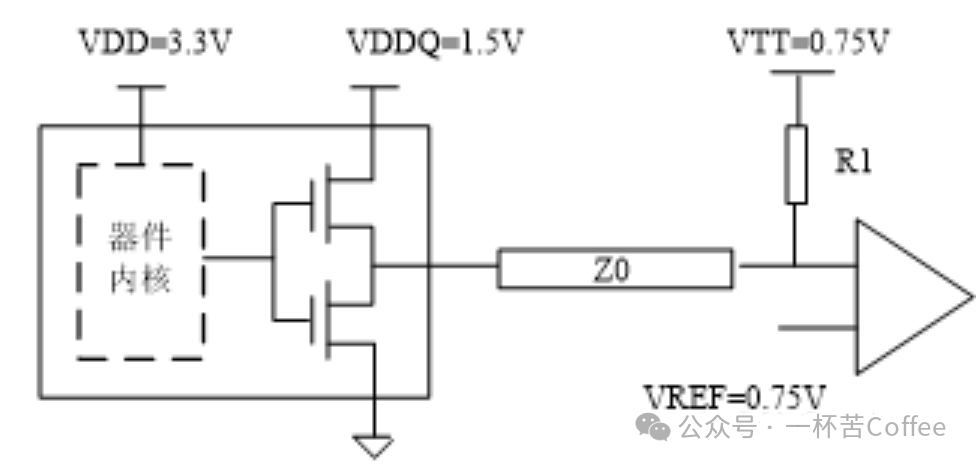

发送同LVCOMS构造相似,接收端采用VREF,具有更小的摆幅和速度。

单端单向模式

差分单向模式

1、SSTL基本电路结构

如下图为SSTL逻辑的单端输出、差分输入电路结构;

1. 输出结构与LVTTL驱动并无差别,通过上下晶体管的轮流导通输出高、低电平;

2. SSTL输入是差分结构,因此输入提供了比较好的电压增益以及稳定的阈值电压,具有更小的输入电压摆幅,和更高的可靠性;

——如上右图所示,In与Vref形成差分输入,Vref一般取值为VDDQ/2(举例:VDDQ = 1.8V,那Vref = 0.9V)。

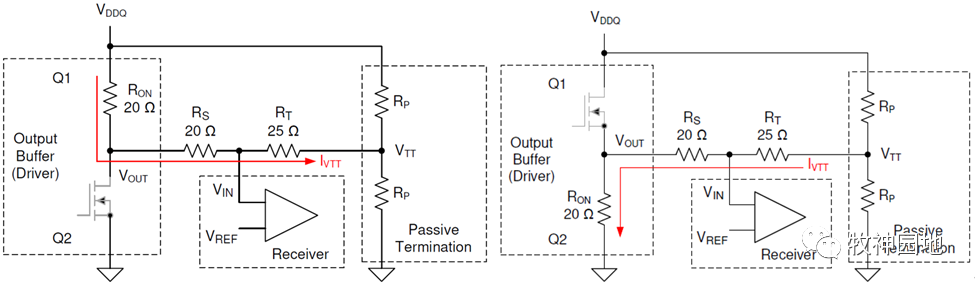

3. 如下图所示为SSTL输出到输入拓扑,需要在终端外部上拉至VTT,一般取VDDQ/2;保证输出阻抗Rs = 线路阻抗Z0;上拉电阻RT用于线路阻抗匹配:RT = Z0;

——因为VTT终端会吸收电流,接收器输入电压(VIN)高于VREF;当输出缓冲器处于低状态时(上管关断且下管导通),电流通过VTT端源电流RT和RS从VTT流向地,从而VIN小于VREF。

如下图所示为SSTL电平输出为高的情况(以SSTL_18为例),Q1导通电阻RON典型值为20Ω与Rs组合成为源端匹配,两个Rp分压得到VTT与RT配合成为终端匹配阻抗;

(1)输出为高时,电流方向为:VDDQàRONàRsàRTàVTT;所以此时VIN输入端的电压要高于VTT;

(2)输出为低时,电流方向为:VTT à RTàRsàRONà GND;此时VIN输入端的电压要低于VTT。

——数据输出高电平或低电平状态:1,如果输出高电平和低电平的数量完全相等,那么来自高电平向的VTT电流等于来自低电平的源电流;因此,净VTT电流为零,即VTT电压保持Rp分压;2,如果输出高低电平的数量不等,那么VTT将不再是1/2 VDDQ;具体VTT电平取决于Rp的值和平均电流。

——VTT电压电流有流入和流出两个方向,所以由LDO提供VTT的话有特殊要求,必须要求:既能输出电流,又能吸收电流。

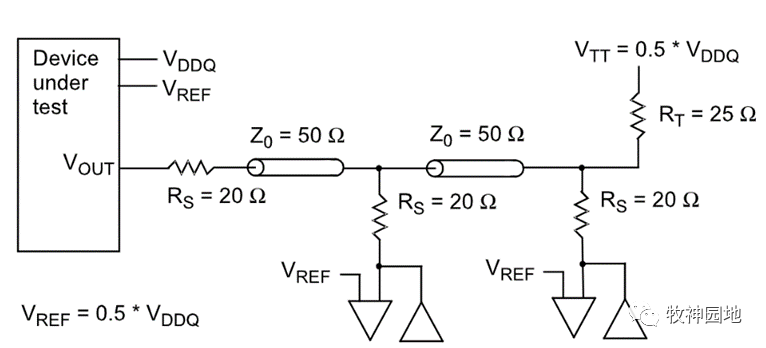

一般情况下,DDR总线都不会只是1驱1的情况,而是1个控制器驱动很多片DDR颗粒;如下图所示线路匹配方式;

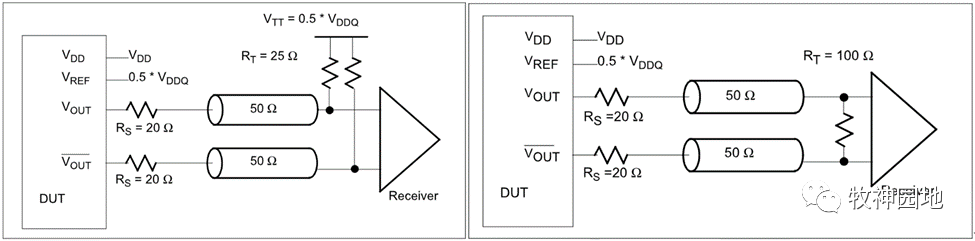

差分信号输入匹配总共有两种方式,如下图所示。

(1)如下左图所示,单端匹配:25Ω上拉到VTT;

(2)如下右图所示,差分匹配:100Ω并联在差分信号之间。

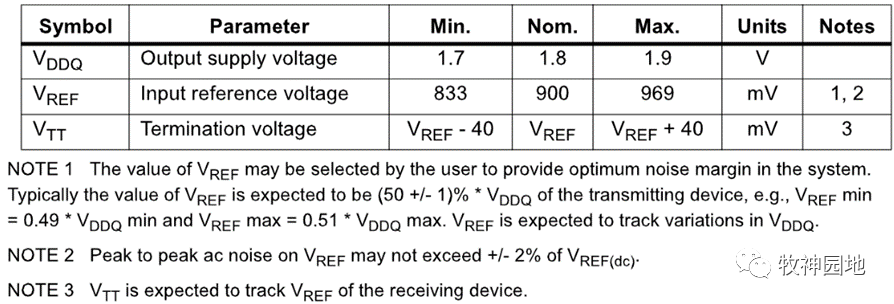

VREF和VTT的电压取值范围如下图所示(以SSTL_18为例),VREF是以(1/2) *VDDQ为基准,而VTT以VREF为基准。

——我们在实际设计中看到的是,如果VREF和VTT都用分立电阻来搭,那么VREF用1K±1%分压至(1/2) *VDDQ,而VTT则用Rp分压至(1/2) *VDDQ;它们俩追踪的都是(1/2) *VDDQ。

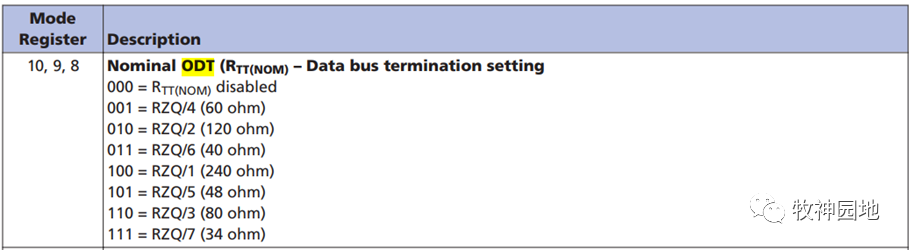

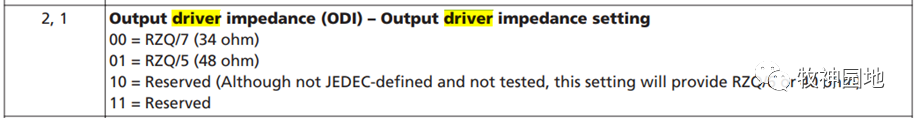

在DDR SDRAM的实际设计中,我们并没有连接Rs和RT电阻,是怎么回事呢?因为实际DDR设计中,为了简化DDR SDRAM的硬件设计,已经将能集成进芯片的都集成进去了;如下图所示:ODT(数据总线终端匹配电阻设置)和ODI(输出驱动阻抗设置)。

2、SSTL电平分析

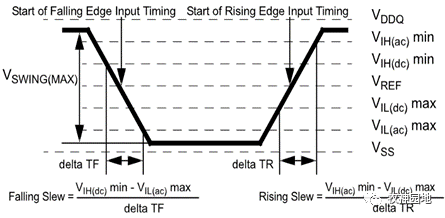

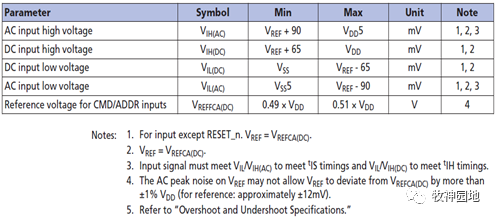

1. 如下图所示为DDR4单端(Single-ended)信号的电平标准;

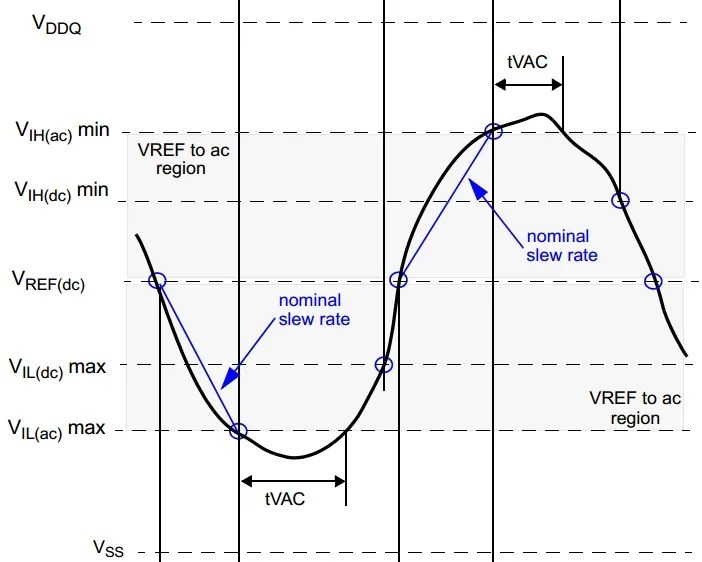

2. 高/低电平有两个电平标准: AC和DC;当信号穿越AC值时确立了信号进入了高/低电平,而当信号反向穿越DC值时才能用该电平状态离开;

——举例,如下图VIH(AC) = VREF+90mv,而VIH(DC) = VREF+65mv;所以当信号从低跳变到高电平时,必须穿越VIH(AC)才能确立高电平状态,而当信号在高电平波动时,只要不跌穿VIH(DC),那么认为其高电平是稳定的;这点同普通的CMOS或TTL电平有很大的不同。

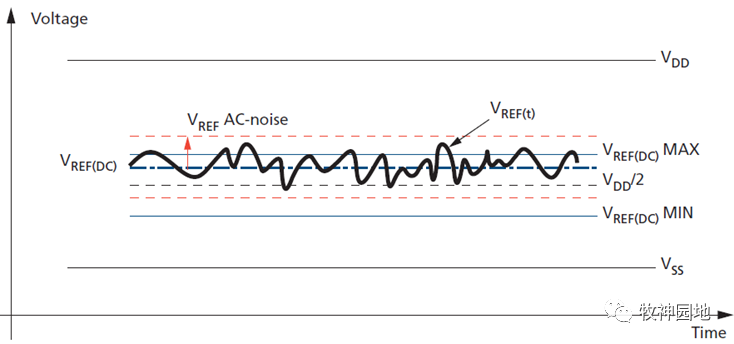

2, 如图所示,其参考电平是VREF

VREFCA:表示对地址、控制、命令信号参考标准;

VREFDQ:表示对数据线参考标准;

对VREF的要求如下图所示。

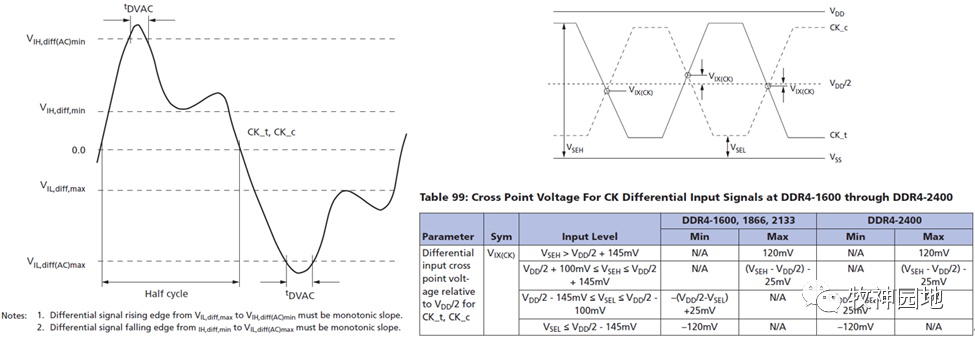

2. 如下图所示为DDR4差分(Differential-ended)信号的电平标准:CK_t/CK_c时钟信号(DQ/DQS类似)。

1, 如下左图为差分信号的判断标准,同样有AC和DC的电平要求;

2, 对差分信号的电平要求之外,还有两个单端时钟交叉点的位置要求。

-

HSTL

全称 The high-speed transceiver logic 高速传输逻辑。常应用在1000phy,和存储器中。结构和SSTL类似。

CLASS-1只有输入有戴维南模式,输出没有,且只支持单项传输。

CLASS-2输出和输出都支持戴维南模式,且支持双向传输。

HSTL和SSTL 输入和输出端端接必须存在,不可以分时处理。

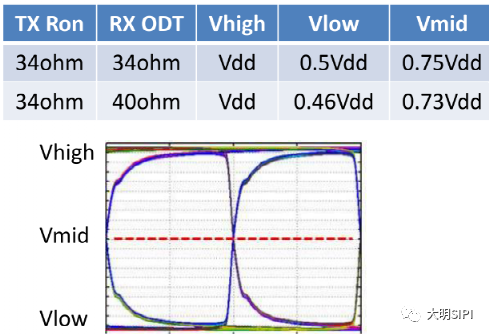

以图为例,假设源端电阻为25Ω,则信号线上的直流电压VDC=0.25V

当输出为VDDQ时,到负载端的电压VAC=0.5+VDC=0.75V

当输出为GND时,到负载的电压VAC=0.25V

1、HSTL基本电路结构

输入输出结构基本上和SSTL相同

HSTL共有四种电平:

-

供电电压VDD:可能为1.5V、1.8V、2.5V、3.3V。

-

输出Buffer电压VDDQ:典型值为1.5V,直接决定了差模电压为1.5V。

-

接收器的参考电压VREF:通常为VDDQ的1/2,根据接收端Buffer、短接方式不同,VREF电压也有可能不同。VREF电压对噪声要求非常严格,一般要求控制在1%~2%以内。

-

端接电压VTT:这个电压是非必须的,有些芯片内部可能会集成片上端接,对于地址控制线在拓扑结构简单的情况下完全可以采用源端匹配或者直连的方式实现。

2、HSTL电平分析

HSTL的输入逻辑电平定义了两个值:AC值和DC值。

-

AC值

AC值表明了接收器必须满足的时序规范电平,即只有信号的边沿超过了AC电平值才会被认为是有效电平。

-

DC值

DC电平的意义就在于清晰的定义最终的逻辑状态,也就是说信号在维持稳定电平时只有高电平不跌落到VIH(DC)的最小值以下、低电平不超过到VIL(DC)的最大值以上就能够保证接收器能够正确的接收数据。

HSTL电平单端输入逻辑

| 参数 |

最小值 |

最大值 |

单位 |

| VIH(DC) |

VREF+0.1 |

VDDQ+0.3 |

V |

| VIL(DC) |

VSS-0.3 |

VREF-0.1 |

V |

| VIH(AC) |

VREF+0.2 |

/ | V |

| VIH(AC) |

/ | VREF-0.2 |

V |

HSTL电平也支持差分输入,相比单端信号需要额外关注的参数为差分幅值VDIF(AC)\ VDIF(DC)、共模噪声VCM(DC)、以及交叉点的范围VX如下表所示:

HSTL电平差分输入逻辑

| 参数 | 最小值 | 最大值 | 单位 |

| VCM(DC) |

VSS-0.3 | VDDQ+0.3 | V |

| VDIF(DC) |

0.2 | VDDQ+0.6 | V |

| VCM(AC) |

0.68 | 0.82 | V |

| VDIF(AC) |

0.4 | VDDQ+0.6 | V |

| VX | 0.68 | 0.82 | V |

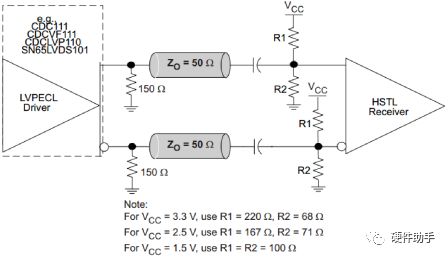

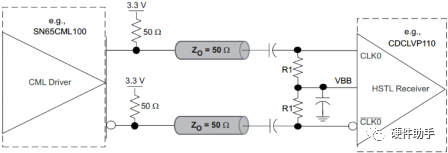

3、LVPECL到HSTL的连接

150Ω电阻用作LVPECL输出的直流偏置(VCC-1.3V),也提供了一个源电流的直流通路。在HSTL接收端,R1和R2被用作戴维南端接,阻抗为50Ω(R1//R2),同时也设定了共模电压(VCM=0.75V)。

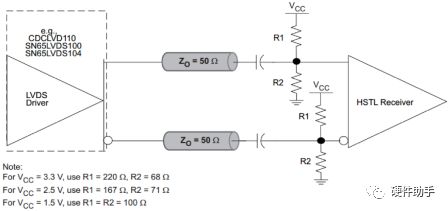

4、LVDS到HSTL的连接

CML和HSTL的互连推荐采用交流耦合。

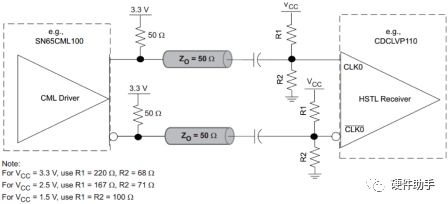

5、CML到HSTL的连接

CML和HSTL的互连推荐采用交流耦合。

-

HSUL

全称 High Speed Unterminated Logic 高速非端接逻辑。常在LPDDR2/3中使用。只是在源端串联匹配,没有在接收端并联匹配,功耗可以做到特别低。

它跟SSTL逻辑一样,也定义了ac和dc电平。

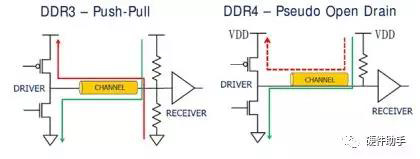

POD

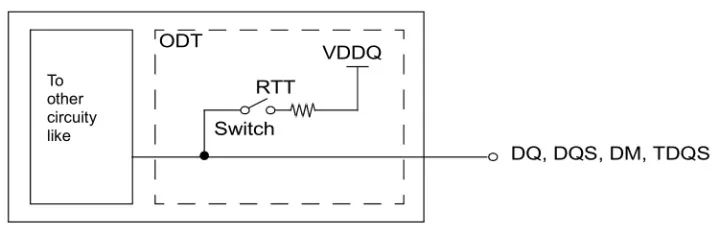

POD是Pseudo Open Drain的缩写,字面理解就是“伪开漏极”电平。那为什么是“伪开漏极”呢?让我们看一下它的结构

左)SSTL电平(右)POD电平

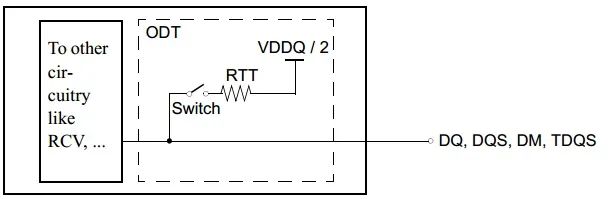

如上图所示,可以看出POD电平的输出电路和SSTL电平并没有差别,差别仅仅在于POD和SSTL电平的所采用的终端端接方式(ODT)和Vref不同。SSTL电平的Vref是固定值0.5倍的VDD,终端采用标准的戴维南端接;而POD电平的Vref是芯片内部确定,外部的端接只用一个上拉电阻。

首先,我们先看Vref。理想的Vref位置应该位于数据眼图的中央,即Vref = Vmid = 0.5*(Vhigh + Vlow)。对于DDR4的数据信号理想的Vref位置示意如下:

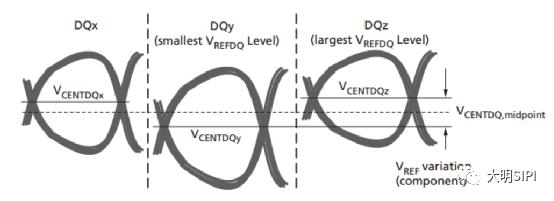

然而在实际中,由于驱动器、传输通道以及ODT的非理性特性,眼图的中央位置很难计算出来。每个DQ信号的驱动、传输通道、和ODT都会有偏差,所以每个DQ的Vref都可能各不相同。因此,需要一种自适应的training机制来寻求最优的Vref。

这种自适应的training机制为DDR4的DQ信号在更低的电平下获得足够的噪声余量提供了有利条件。

由于POD的参考电平Vref大小会随着驱动强度、负载、传输线特性等不同而改变,因此DDR4数据信号的参考电平VrefDQ是由芯片内部自己产生的,没有外接该电平的管脚,只有地址信号的参考电平管脚VrefCA。POD的VrefDQ通过控制寄存器设置值由芯片自行优化调整,称为VrefDQ Training。

另外需要提及的一点是,LPDDR3的内部端接ODT也是上拉到VDDQ。

同时对比SSTL和POD电平,我们可以发现:POD电平只有在低电平时才会有功耗,高电平由于Tx和Rx是等电位的几乎没有电流因此功耗几乎为零。这就是POD电平的另一个优势,使得DQ信号的功耗几乎降低了50%。

驱动端输出低电平时,POD由于上拉电压高,功耗稍大于SSTL,正因此,DDR4多了一个DBI功能,即数据总线翻转,当一个字节里0的位数大于1的位数时,可以将0和1反转,以降低功耗。

智能推荐

python水表识别图像识别深度学习 CNN_水表 深度学习 识别-程序员宅基地

文章浏览阅读551次,点赞8次,收藏8次。重点:项目和文档是本人近期原创所作!程序可以将水表图片里面的数据进行深度学习,提取相关信息训练,lw1.3万字重复15%,可以直接上交那种!具体和看下面的目录。python水表识别,图像识别深度学习 CNN,Opencv,Keras。_水表 深度学习 识别

【DataSet】遥感图像方面的人工智能数据集_群智感知 图像数据集-程序员宅基地

文章浏览阅读288次。遥感图像方面的人工智能数据集数据集类别常用数据集目标检测数据集DSTL 卫星图像数据集;RSOD-Dataset 数据集;NWPUVHR-10地理遥感数据集图像分割数据集Inria AerialImage Labeling Dataset 遥感图像数据集遥感图像分类数据集UCMerced Land-Use Data Set 土地遥感数据集_群智感知 图像数据集

python使用镜像安装opencv_opencv_python安装镜像-程序员宅基地

文章浏览阅读2.9k次,点赞3次,收藏11次。如何在pycharm中安装opencv_opencv_python安装镜像

手把手教你IDEA创建SSM项目结构_idea创建ssm web项目-程序员宅基地

文章浏览阅读595次,点赞2次,收藏8次。我的小站SSM项目需要用来管理依赖,所以我们需要先配置好,配置很容易,我就不演示了。首先,我们新建项目,勾选,选择模板,然后创建。这里耐心等待下载完成。可以看到,这里没用相关的文件夹。我们直接在文件夹上右键新建文件夹,下面会显示一个,直接创建就可以。此时,我们按照规范来,创建一个包。项目结构多种多样,比如三层架构啥的,按照你的需求来。我这里就稍微演示一下。这里这些结构都是可以自己按照规范命名,结构也有很多,分层架构方法也有很多,这里权当借鉴一下。我这里整合了一份依赖,如需使用可按照自己需求和对于版本进_idea创建ssm web项目

2022年-2023年中职网络安全web渗透任务整理合集_server2280 中职组-程序员宅基地

文章浏览阅读3.2k次。2022年-2023年中职网络安全web渗透任务整理合集_server2280 中职组

攻防世界_难度8_happy_puzzle_攻防世界困难模式攻略图文-程序员宅基地

文章浏览阅读645次。这个肯定是末尾的IDAT了,因为IDAT必须要满了才会开始一下个IDAT,这个明显就是末尾的IDAT了。,对应下面的create_head()代码。,对应下面的create_tail()代码。不要考虑爆破,我已经试了一下,太多情况了。题目来源:UNCTF。_攻防世界困难模式攻略图文

随便推点

WPF TabControl 滚动选项卡_wpf 使用tabcontrol如何给切换的页面增加滚动条-程序员宅基地

文章浏览阅读1.3k次,点赞27次,收藏19次。我原本以为是很简单的事情,但是没想到实际做起来还是有很多的基础知识点的。我们平常写TabControl的时候,可能都很习惯了直接写TabControl+TabItem。但是TabControl负责了什么布局,TabItem负责了什么布局,我们都不知道。在《深入浅出WPF》中,我们可以看到TabControl属于ItemsControl我们去看看控件模板样式副本。WPF的xaml的优点是每个控件都是单独的逻辑,耦合低。缺点是写起来麻烦,每次改动约等于重新写一个新的。通过增加自己的工作量来降低了耦合我们可以看_wpf 使用tabcontrol如何给切换的页面增加滚动条

Apache Jmeter常用插件下载及安装及软硬件性能指标_jmeter插件下载-程序员宅基地

文章浏览阅读2.1k次,点赞24次,收藏47次。Apache Jmeter常用插件下载及安装_jmeter插件下载

SpringBoot 2.X整合Mybatis_springboot2.1.5整合mybatis不需要配置mapper-locations-程序员宅基地

文章浏览阅读5.9k次,点赞6次,收藏18次。实际上Mybatis的整合过程像极了我们程序员的一生。在SpringBoot 整合Mybatis之前,我们回忆回忆以前 MyBatis 单独使用时,myBatis 核心配置文件要配置数据源、事务、连接数据库账号、密码....是的全是这货一个人干,都要亲力亲为。这就是我们的低谷期myBatis 与 spring 整合的时候,配置数据源、事务、连接数据库的账号什么的都交由 spring 管理就行,就不用什么都自己管理自己去干。这就是我们春风得意的时候,事业有着落...再后来,Spring_springboot2.1.5整合mybatis不需要配置mapper-locations

ios刷android8.0,颤抖吧 iOS, Android 8.0正式发布!-程序员宅基地

文章浏览阅读162次。原标题:颤抖吧 iOS, Android 8.0正式发布!如果现在选一个最好用的手机操作系统,多数人还是认为 iOS。不过最近几年,苹果和安卓的竞争越来越激烈,苹果的优势也越来越小。眼看 Android 8.0 就要来了,下面就让我们扒一扒 Android 8.0 到底有哪些更新? 后台限制机制,从此告别卡顿安卓手机比较坑爹的一个地方就是后台越多应用,就会越卡顿,导致用户需要偶尔清理后台,一定程度..._苹果刷安卓8

【halcon】C# halcon 内存暴增_halcon 读二维码占内存-程序员宅基地

文章浏览阅读344次。如果不使用halcon引擎,直接调用lines_gauss虽然内存会飙升,但是属于图片占用的内存还是会立刻被释放,但是如果在halcon引擎中,这个就会释放很慢,如果连续处理图片,你的内存就会“爆炸”!一个6M的图片通过halcon进行加载,大约会消耗200M的内存,如果等待GC回收,而你又在不停的读取图片,你的内存占用,将在短时间内飙升。目前给我的感觉是,如果我封装了一个算子,然后通过halcon引擎调用,然后这个算子需要传入图片参数,这个图片传入引擎后,过很久才会被释放掉。_halcon 读二维码占内存

Thinkpad X250 secure boot failed 启动失败问题解决_安装完系统提示secureboot failure-程序员宅基地

文章浏览阅读304次。Thinkpad X250笔记本电脑,装的是FreeBSD,进入BIOS修改虚拟化配置(其后可能是误设置了安全开机),保存退出后系统无法启动,显示:secure boot failed ,把自己惊出一身冷汗,因为这台笔记本刚好还没开始做备份.....根据错误提示,到bios里面去找相关配置,在Security里面找到了Secure Boot选项,发现果然被设置为Enabled,将其修改为Disabled ,再开机,终于正常启动了。_安装完系统提示secureboot failure